[2025/11/20] Our student Yuyang Cui has got the CSC scholarship for abroad study. She will go to CNRS TIMA Lab. in Grenoble, France the next year. Congrats. to Yuyang!

[2025/11/9] Our article "ConvGA: Convolution Network Guided Genetic Algorithm for Optimal PDN Decoupling Design" was accepted by IEEE Trans. on CAD (CCF-A), Congrats. to Yuchuan!

[2025/10/29] Our article "Folivora: Ultra Low Power Microprocessor Design with Nano Electro-mechanical Relay and Nanotube Memory" was accepted by IEEE Trans. on CAD (CCF-A), Congrats. to Siyuan!

[2025/10/15] Our paper "Inter-chip Clock Network Synthesis on Passive Interposer of 2.5D Chiplet Considering Transmission Line Effect" was accepted by IFIP/IEEE VLSI-SoC 2026,Congrats. to Yiyu and Tai Yan!

[2025/09/05] Our two papers "Full-Chip Thermal Map Estimation by Multimodal Data Fusion via Denoising Diffusion" and "Φ-BO: Physics-Informed Bayesian Optimization for Multi-Port Decoupling Capacitor Placement in 2.5-D Chiplets" were accepted by ASPDAC (CCF-C) 2026,Congrats. to Jing Li, Quansen and Yuchuan!

[2025/6/20] 3 students graduated from CADET lab. Longze Wang(HiSilicon),Tai Yan(South Grids),Peng Xie(OmniVision), Congrats. to them!

[2025/6/15] Our article“ASAP: Accelerating Corner-based Timing Analysis with Bayesian Active Self-Attention Neural Process”was accepted by IEEE Trans. on CAD(CCF-A). Congrats. to Longze!

[2025/6/10] Our article "Testing and Fault Tolerance Techniques for Carbon Nanotube-Based FPGAs" was accepted by Integration, the VLSI Journal, Congrats. to Siyuan!

[2025/5/14] Our two papers“Inductive Effect-Aware Power Distribution Network Modeling and Analysis for Heterogeneous 3D Integrated Circuits" and "PV-Clock: Process Variation-Aware 3D Clock Network Synthesis for Robust and Power-Efficient Timing Optimization" were accepted by IEEE Computer Society Anuual Symposium on VLSI (ISVLSI 2025), Congrats to Yiyu and Quansen!

[2025/5/12] Prof. Cheng was invited to give a talk on International Symposium on EDA (ISEDA 2025) Tutorial session, and the title is "VLSI Physical Design, From 2D to 3D". Sponsored by IEEE CEDA, Prof. Cheng and Prof. Wenjian Yu from Tsinghua Univ. organized ISEDA CEDA adjoint special session "Deep Learning Inspired Algorithms for Physical Modeling and Analysis of Advanced IC Design". Quansen, Yiyu and Yuyang attended the conference as well.

[2025/5/6] Our article“Carbon Nanotube Interconnect Optimizations with Bayesian Neural Network and Bayesian Optimization”was accepted by IEEE Transactions on CAD (CCF-A), Congrats to Zhelong!

[2025/3/30] 课题组两篇论文“Cool3D: Cost-Optimized and Efficient Liquid Cooling for 3D Integrated Circuits”和“A Comprehensive Inductance-aware Modeling Approach to Power Distribution Network in Heterogeneous 3D Integrated Circuits"被欧洲EDA顶会DATE录用。祝贺李婧和泉森!

成元庆副教授与TU/e的Aida Todri教授合影

李婧在DATE上做大会报告,汇报课题组工作

[2025/1/10] 课题组论文“T-Fusion: Thermal Modeling of 3D ICs with Multi-fidelity Fusion”被EDA权威会议ASPDAC录用。祝贺秉睿!

[2024/11/30] 课题组与邢炜老师以及Vasilis Pavlidis教授合作论文“ARO: Autoregressive Operator Learning for Transferable and Multi-fidelity 3D-IC Thermal Analysis with Active Learning”被国际EDA顶会ICCAD录用。祝贺明月和伟恒!

[2024/11/10] 成元庆副教授出席在香港举行的ASPDAC程序委员会会议并在专题研讨会上介绍课题组的成果。

与Georgia Tech的Sun-Kyu Lim教授合影

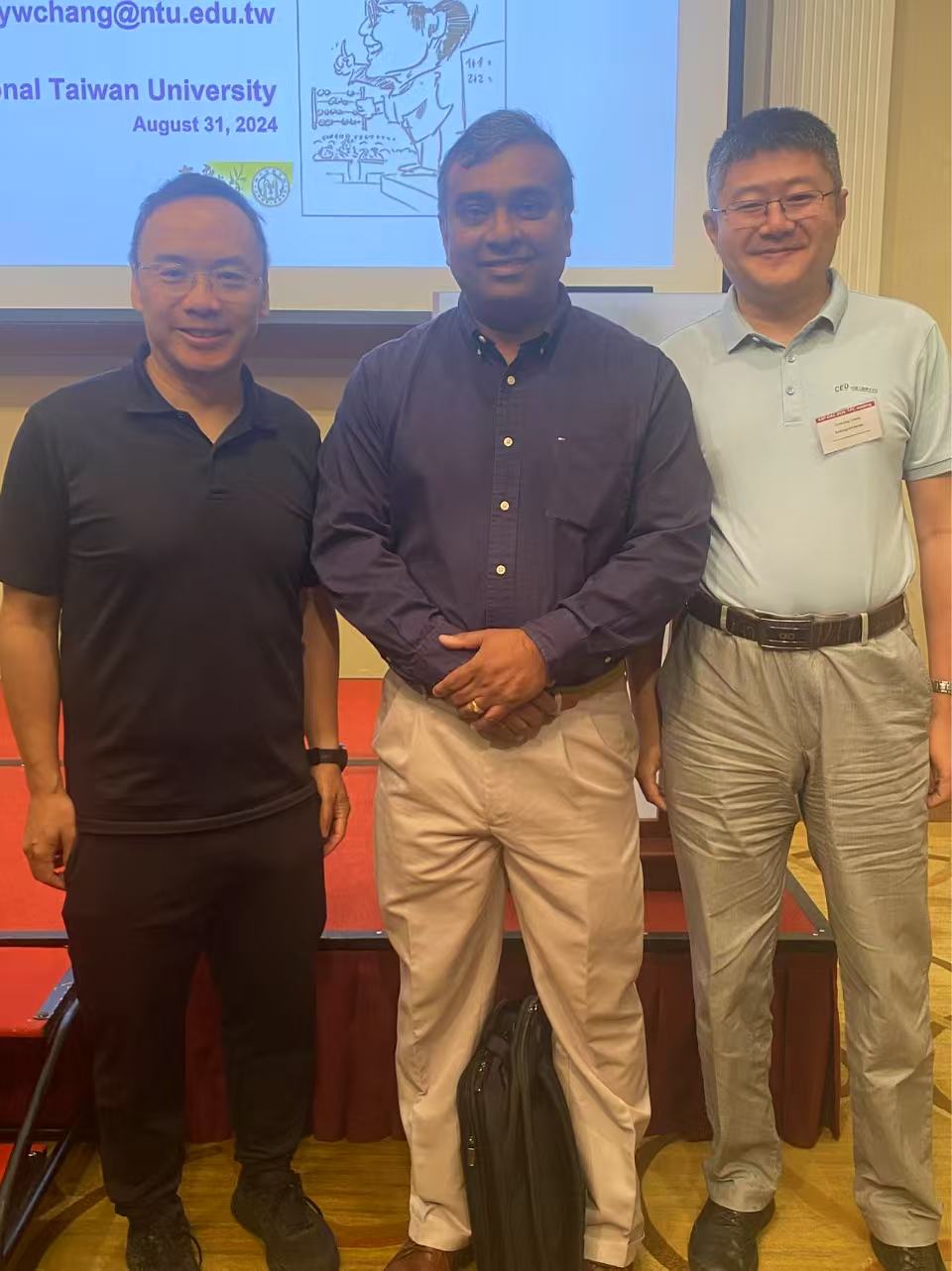

与HKUST的谢源教授以及ASU的Krish Chakarabarty教授合影

[2024/7/15] 课题组与邢炜老师合作文章“MAUnet: Multiscale Attention U-Net for Effective IR Drop Prediction”被EDA顶会IEEE/ACM Design Automation Conference录用。祝贺明月、雅阁和科霖!

[2024/7/8] 成元庆副教授在欧盟Erasmus+计划资助下,对希腊亚里士多德大学进行为期1周的学术访问,并商讨双发合作计划。

成元庆副教授与Georgios Kramidas教授课题组合影

[2024/7/2] 成元庆副教授在希腊沃洛斯召开的SMACD会议上组织Tutorial "Machine Learning for Design Automation".

成元庆副教授在大会上进行技术报告

成元庆副教授与Vasilis Pavlidis教授课题组合影

[2024/1/27] 课题组文章"Multi-Corner Timing Analysis Acceleration forIterative Physical Design of ICs"被IEEE Trans. on CAD录用. 感谢龙泽和喆龙的辛勤工作,也感谢邢炜老师的通力合作!

[2024/1/27] 成元庆副教授在ASPDAC2024上做题为"BoCNT: A Bayesian Optimization Framework for Global CNT Interconnect Optimization"论文报告。论文的第一作者为吴航同学。祝贺吴航同学!也感谢徐宁老师和邢炜老师的大力支持!

成元庆副教授在ASPDAC2024大会上作技术报告

成元庆副教授与张悦教授和参会北航学生合影

成元庆副教授与UCSD的Andrew Kahng教授合影

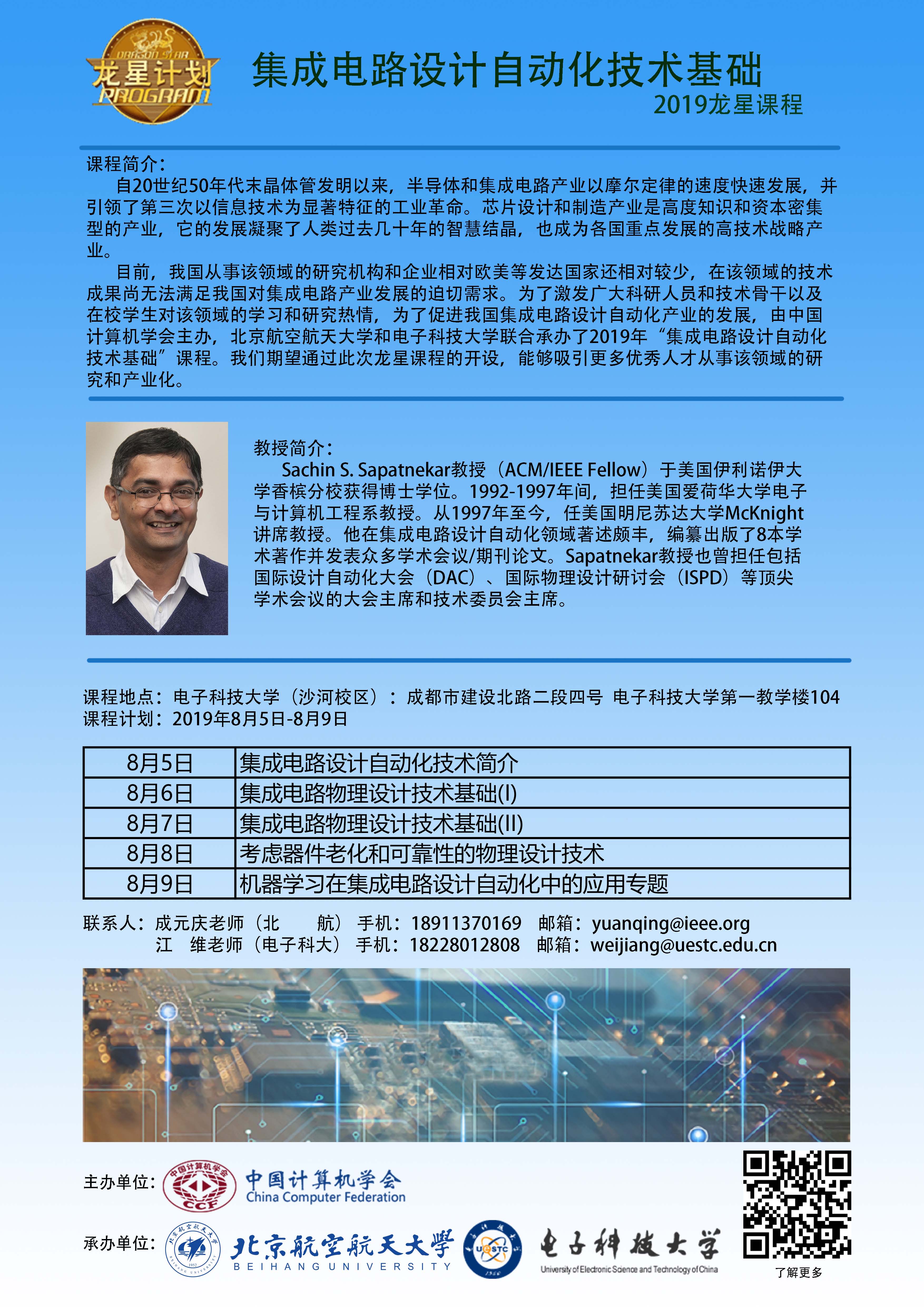

成元庆副教授与明尼苏达大学的Sachin Sapatnekar教授和UT Austin的David Pan教授合影

Due to COVID-19, ISQED was changed to a virtual conference. Prof. Cheng atteded on-line and reported the paper "DOVA: A Dynamic Overwriting Voltage Adjustment for STT-RAM L1 Cache".

Papers titled "SIP: Boosting Up Graph Computing by Separating the Irregular Property Data" and "Zero-skew Clock Network Synthesis for Monolithic 3D ICs with Minimum Wirelength" were accepted by GLVLSI'20. Congrats to Jiacheng and Wei !

[2019/12/4] Our paper is accepted by ISQED2020.

Congratulations to Jinbo and Keren!

[2019/7/20] CCF Dragon Star Course "Introduction to Design Automation of VLSI" will start in UESTC, Chengdu.

The paper titled "An Adaptive Thermal-Aware ECC Scheme for Reliable STT-MRAM LLC Design" was accetped by IEEE Transactions on Very Large Scale Integration (VLSI) Systems. This work is collaborated with Bi Wu from Prof. Weisheng Zhao's group, and Prof. Ying Wang from Institute of Computing Technology, Chinese Academy of Sciences.

Prof. Cheng was invited as the chair of session "Learning gets smarter" in DATE 2019 held in Florence, Italy. DATE conference is one of the premier EDA conferences, which attracts more than 1000 researchers and engineers to attend every year.

The paper titled "A Novel High Performance and Energy Efficient NUCA Architecture for STT-MRAM LLCs with Thermal Consideration" was accepted by IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. This work is collaborated with Bi Wu from Prof. Weisheng Zhao's group, and Prof. Ying Wang from Institute of Computing Technology, Chinese Academy of Sciences.

The proposal "Multi-failure Mechanism Reliability Modeling and Reliable Design for STT-MRAM" gets supported by Beijing Natural Science Fundation with Grant No. 4192035.

Prof. Pavlids from University of Manchester visited CADET lab. The visit is to enhance the collaborations between Prof. Pavlids's group and CADET on the research of monolithic 3D ICs. He will give a five-day short course on 3D IC design during stay in Beihang University.

The proposal titled "Monolithic 3D Integrated Circuit Design with Spintronic Technology was supported by Beihang University with grant No. Z2018004.. The proposal is based on the collaboration between CADET team and the team led by Prof. Vasilis Pavlids from University of Manchester, U.K.

The paper of CADET titled "An Adaptive Thermal-Aware ECC Scheme for Reliable STT-MRAM LLC Design", collaborating with Bi Wu from Prof. Weisheng Zhao's group, was selected as Work-In-Progress poster on DAC'2018. Prof. Cheng presented this work and took a photo with David Patterson - the 2018 ACM Turing Award winner:)

Chen Liu from CADET Lab. presented our group's paper titled "NEAR: a Novel Energy Aware Replacement Policy for STT-MRAM LLCs" on ISCAS'2018 conference.

The paper of Prof. Cheng's group collaborated with Prof. Weisheng Zhao's group titled "Write energy optimization for STT-MRAM cache with data pattern characterization" was accepted by ISVLSI 2018 conference.

Bi Wu's paper titled "Chameleon: A Thermally Adaptive Error Correction Code Design for STT-MRAM LLCs" was accepted as Work-in-Progress poster of Design Automation Conference 2018. Congratulations to Bi!

Prof. Yuanqing Cheng's paper, collaborated with Mr. Liuyang Zhang and Prof. Aida Todri-Sanial, titled "Addressing the Thermal Issues of STT-MRAM from Compact Modeling to Design Techniques" was accepted by IEEE Transactions on Nanotechnology.

Chen Liu's paper titled "NEAR: a Novel Energy Aware Replacement Policy for STT-MRAM LLCs" was accepted by 2018 IEEE International Symposium on Circuits and Systems, to be held in Florence, Italy from May 27-30. Congratulations to Chen Liu! Good job!

Prof. Yuanqing Cheng's paper titled "Power Supply Noise Aware Task Scheduling on Homogeneous 3D MPSoCs Considering the Thermal Constraint" was accepted by Journal of Computer Science and Technology, Springer.

Our group's paper, collaborated with Ms. Linuo Xue and Prof. Yuan Xie, titled "An Adaptive 3T-3MTJ Memory Cell Design for STT-MRAM based LLCs" was accepted by IEEE Transactions on Very Large Scale Integrated Systems. Congratulations to Bi Wu and Beibei!

Bi Wu wins the National Scholarship. Congratulations to Bi Wu!

Our paper titled "Thermosiphon: A Thermal Aware NUCA Architecture for Write Energy Reduction of the STT-MRAM based LLCs" is accepted by ICCAD conference. Congratulations to Bi Wu!

Associate Professor

Supervisor of Doctorate Candidates

Supervisor of Master's Candidates

E-Mail:

Date of Employment:2013-12-01

School/Department:集成电路科学与工程学院

Education Level:博士研究生

Business Address:209, The 1st Building, Xueyuan Road Campus, Beihang University.

Gender:Male

Contact Information:010-82339539

Degree:博士

Status:Employed

Academic Titles:CCF Senior Member,IEEE Senior Member,IEEE CEDA Beijing Chapter Treasurer

Other Post:ICCAD/DATE/ASPDAC TPC Member,Integration, the VLSI Journal Associate Editor

Alma Mater:Institute of Computing Technology, CAS

Discipline:Computer Science and Technology

Electronic Science and Technology

Honors and Titles:

带领学生获得EDA精英挑战赛全国二等奖 2023-11-23

带领学生获得EDA精英挑战赛全国一等奖 2022-11-24

带领学生获得全国集成电路创新创业大赛全国一等奖 2024-07-22

ASPDAC2020 三维集成电路论坛 “卓越组织奖” 2020-01-31

北京市科学技术奖二等奖 2017

北京航空航天大学“蓝天新秀” 2017

The Last Update Time : ..